# Composing circuits

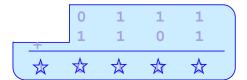

### 4-bit Ripple-Carry Adder

8 input bits

$\Rightarrow$  5 output bits  $\stackrel{\wedge}{\Rightarrow}$

Now let's make lots of them!!

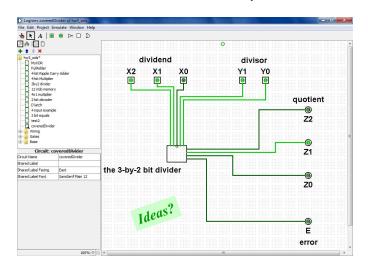

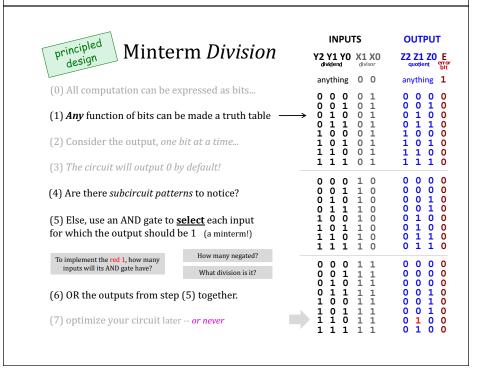

# Division? hw6pr3

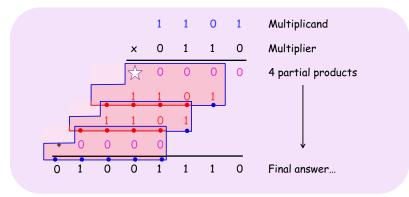

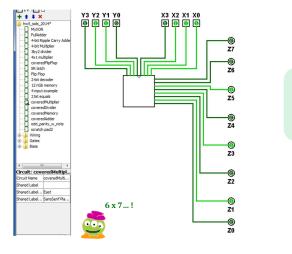

## hw6pr2: A 4-bit multiplier

(A1) The AND gate is *single-bit* multiplication.

(A2)  $\stackrel{\wedge}{>} == 0$

(A1) Use a 4x1-bit helper circuit to find the four partial products...

(A3) You need three (3) ripple-carry adders to finish: see above...

## Time-optimized circuits: *Carry lookahead adders*

The following circuit is called a carry lookahead adder.

By adding more hardware, we reduced the number of levels in the circuit and sped things up.

We can "cascade" carry lookahead adders, just like ripple carry adders. We'd have to do carry lookahead between the adders too.

#### How much faster is this?

For a 4-bit adder, not much. There are 4 gates in the longest path of a carry lookahead adder, versus 9 gates for a ripple carry adder.

But if we do the cascading properly, a 16-bit carry lookahead adder could have only 8 gates in the longest path, as opposed to 33 for a ripple carry adder.

Newer CPUs these days use 64-bit adders. That's 12 vs. 129 gates or 10x speedup!

The delay of a carry lookahead adder grows *logarithmically* with the size of the adder, while a ripple carry adder's delay grows *linearly*.

The thing to remember about this is the **trade-off between complexity and performance**. Ripple carry adders are simpler, but slower. Carry lookahead adders are faster but more complex.

# Half a computer: the CPU

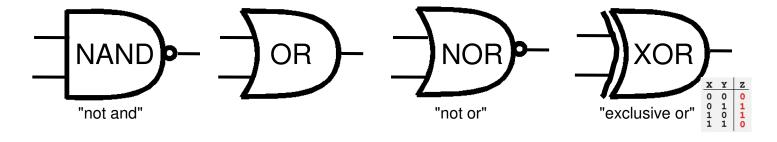

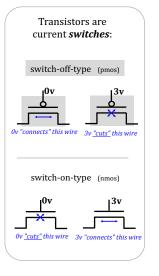

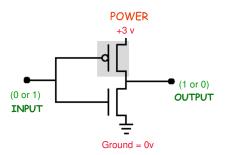

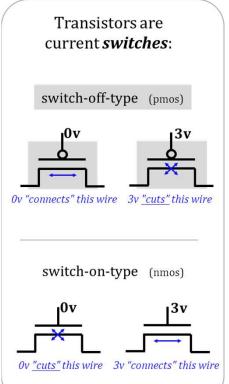

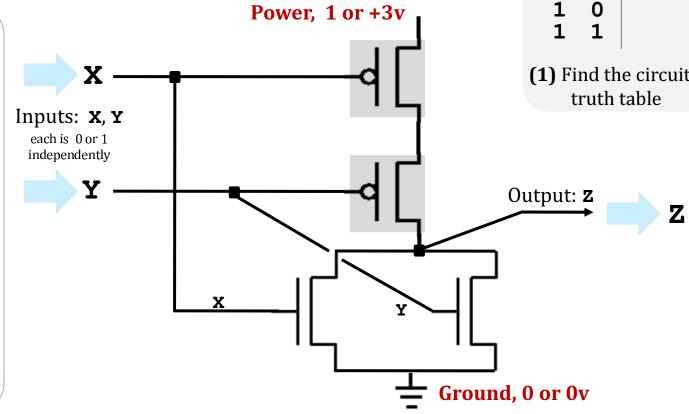

# transistors ↓ gates ↓ arithmetic

## Building a NOT gate

Building a **NOT** gate from transistors...

For systems, a face-lift is to add an edge that *creates a cycle*, not just an additional node.

- also Alan Perlis

For systems, a face-lift is to add an edge that *creates a cycle*, not just an additional node.

- also Alan Perlis

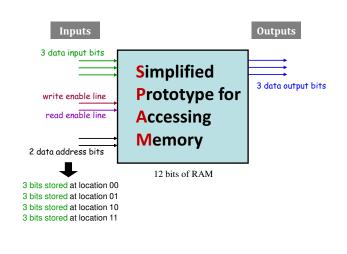

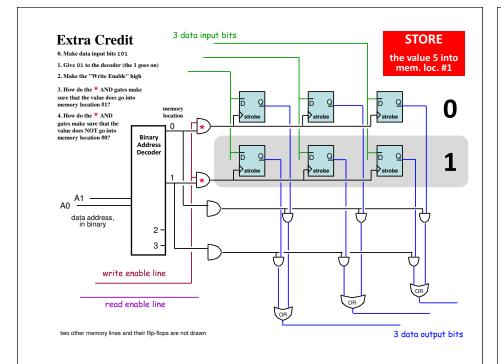

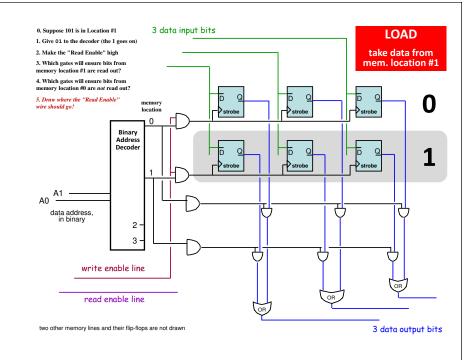

# Random Access Memory

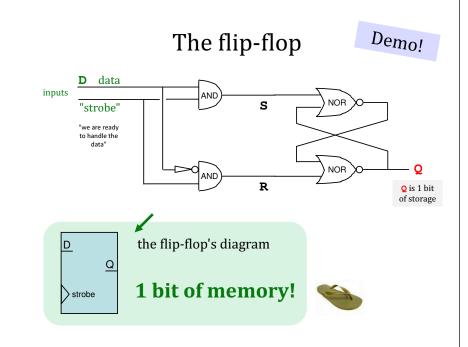

Demo!

Extra this week: **Design 12nGbits of RAM**

Name(s) \_

(1) Find the circuit's

(3) Extra! How could you alter the transistor-level design to make an AND?

(2) the above circuit is one of these gates – *which one*?